### NONRESIDENT TRAINING COURSE

January 2012

# Navy Electricity and Electronics Training Series

Module 13-Number Systems and Logic Circuits

NAVEDTRA 14185A

S/N 0504LP1113098

Notice: NETPDTC is no longer responsible for the content accuracy of the NRTCs.

For content issues, contact the servicing Center of Excellence: Center for Surface Combat Systems; (540) 284-1061 or DSN: 234.

For course registration, issues, or login issues contact the NRTC Helpdesk at: 1-877-264-8583 DSN: 922-1511 or Email: NRTC@navy.mil

DISTRIBUTION STATEMENT A: Approved for public release; distribution is unlimited.

Although the words "he," "him," and "his" are used sparingly in this course to enhance communication, they are not intended to be gender driven or to affront or discriminate against anyone.

DISTRIBUTION STATEMENT A: Approved for public release; distribution is unlimited.

#### **PREFACE**

By enrolling in this self-study course, you have demonstrated a desire to improve yourself and the Navy. Remember, however, this self-study course is only one part of the total Navy training program. Practical experience, schools, selected reading, and your desire to succeed are also necessary to successfully round out a fully meaningful training program.

**THE COURSE**: This self-study course is organized into subject matter areas, each containing learning objectives to help you determine what you should learn along with text and illustrations to help you understand the information. The subject matter reflects day-to-day requirements and experiences of personnel in the rating or skill area. It also reflects guidance provided by Enlisted Community Managers (ECMs) and other senior personnel, technical references, instructions, etc., and either the occupational or naval standards, which are listed in the *Manual of Navy Enlisted Manpower Personnel Classifications and Occupational Standards*, NAVPERS 18068.

**THE QUESTIONS**: The questions that appear in this course are designed to help you understand the material in the text.

**VALUE**: In completing this course, you will improve your military and professional knowledge. Importantly, it can also help you study for the Navy-wide advancement in rate examination. If you are studying and discover a reference in the text to another publication for further information, look it up.

2012 Edition

Published by Center for Surface Combat Systems (CSCS)

NAVSUP Logistics Tracking Number 0504-LP-111-3098

UNCLASSIFIED

### Sailor's Creed

"I am a United States Sailor.

I will support and defend the Constitution of the United States of America and I will obey the orders of those appointed over me.

I represent the fighting spirit of the Navy and those who have gone before me to defend freedom and democracy around the world.

I proudly serve my country's Navy combat team with honor, courage and commitment.

I am committed to excellence and the fair treatment of all."

### TABLE OF CONTENTS

| CHAPTER                      | <b>PAGE</b> |

|------------------------------|-------------|

| 1 Number Systems             | 1-1         |

| 2 Fundamental Logic Circuits | 2-1         |

| 3 Special Logic Circuits     | 3-1         |

| APPENDIX                     |             |

|                              |             |

| A Glossary                   | A-1         |

| B Logic Symbols              | B-1         |

Course Assignments follow Appendix B

### NAVY ELECTRICITY AND ELECTRONICS TRAINING SERIES

The Navy Electricity and Electronics Training Series (NEETS) was developed for use by personnel in many electrical and electronic-related Navy ratings. Written by, and with the advice of, senior technicians in these ratings, this series provides beginners with fundamental electrical and electronic concepts through self-study. The presentation of this series is not oriented to any specific rating structure, but is divided into modules containing related information organized into traditional paths of instruction.

The series is designed to give small amounts of information that can be easily digested before advancing further into the more complex material. For a student just becoming acquainted with electricity or electronics, it is highly recommended that the modules be studied in their suggested sequence.

Considerable emphasis has been placed on illustrations to provide a maximum amount of information. In some instances, knowledge of basic algebra may be required.

Course descriptions and ordering information may be found at <a href="https://www.netc.navy.mil">https://www.netc.navy.mil</a> then click on the Programs tab, then select the Nonresident Training Courses from the list.

Throughout the text of this course and while using technical manuals associated with the equipment you will be working on, you will find the below notations at the end of some paragraphs. The notations are used to emphasize that safety hazards exist and care must be taken or observed.

#### WARNING

AN OPERATING PROCEDURE, PRACTICE, OR CONDITION, ETC., WHICH MAY RESULT IN INJURY OR DEATH IF NOT CAREFULLY OBSERVED OR FOLLOWED.

#### **CAUTION**

AN OPERATING PROCEDURE, PRACTICE, OR CONDITION, ETC., WHICH MAY RESULT IN DAMAGE TO EQUIPMENT IF NOT CAREFULLY OBSERVED OR FOLLOWED.

#### **NOTE**

An operating procedure, practice, or condition, etc., which is essential to emphasize.

### STUDENT FEEDBACK AND QUESTIONS

We value your suggestions, questions, and criticisms on our courses. If you would like to communicate with us regarding this course, we encourage you, if possible, to use e-mail or to post your comments on the Community of Practice (COP) page located at <a href="https://wwwa.nko.navy.mil/portal/home/">https://wwwa.nko.navy.mil/portal/home/</a>. If you write or fax, please use a copy of the Student Comment form that follows this page.

#### For subject matter questions:

E-mail: <u>dlgr\_cscs\_pqs@navy.mil</u> Phone: Comm: 540-284-1061

DSN: 234-4639

Address:

COMMANDING OFFICER Center for Surface Combat Systems 5395 First St Dahlgren, VA 22448-5200

### **Student Comments**

| nit:           |

|----------------|

| State/FPO: Zip |

|                |

**Privacy Act Statement:** Under authority of Title 5, USC 301, information regarding your military status is requested in processing your comments and in preparing a reply. This information will not be divulged without written authorization to anyone other than those within DOD for official use in determining performance.

This page left intentionally blank.

vii UNCLASSIFIED

#### 1 NUMBER SYSTEMS

#### LEARNING OBJECTIVES

After you finish this chapter, you should be able to do the following:

- 1. Recognize different types of number systems as they relate to computers.

- 2. Identify and define unit, number, base/radix, positional notation, and most and least significant digits as they relate to decimal, binary, octal, and hexadecimal number systems.

- 3. Add and subtract in binary, octal, and hexadecimal number systems.

- 4. Convert values from decimal, binary, octal, hexadecimal, and binary-coded decimal number systems to each other and back to the other systems.

- 5. Add in binary-coded decimal.

#### 1.1 INTRODUCTION

How many days' leave do you have on the books? How much money do you have to last until payday? It doesn't matter what the question is if the answer is in dollars or days or cows, it will be represented by numbers.

Just try to imagine going through one day without using numbers. Some things can be easily described without using numbers, but others prove to be difficult. Look at the following examples:

I am stationed on the aircraft carrier *Nimitz*.

He owns a green Chevrolet.

The use of numbers wasn't necessary in the preceding statements, but the following examples depend on the use of numbers:

I have \$25 to last until payday.

I want to take 14 days' leave.

You can see by these statements that numbers play an important part in our lives.

#### 1.2 BACKGROUND AND HISTORY

Man's earliest number or counting system was probably developed to help determine how many possessions a person had. As daily activities became more complex, numbers became more important in trade, time, distance, and all other phases of human life.

As you have seen already, numbers are extremely important in your military and personal life. You realize that you need more than your fingers and toes to keep track of the numbers in your daily routine.

Ever since people discovered that it was necessary to count objects, they have been looking for easier ways to count them. The abacus, developed by the Chinese, is one of the earliest known calculators. It is still in use in some parts of the world.

Blaise Pascal (French) invented the first adding machine in 1642. Twenty years later, an Englishman, Sir Samuel Moreland, developed a more compact device that could multiply, add, and subtract. About 1672, Gottfried Wilhelm von Leibniz (German) perfected a machine that could perform all the basic operations (add, subtract, multiply, divide), as well as extract the square root. Modern electronic digital computers still use von Liebniz's principles.

#### 1.3 MODERN USE

Computers are now employed wherever repeated calculations or the processing of huge amounts of data is needed. The greatest applications are found in the military, scientific, and commercial fields. They have applications that range from mail sorting, through engineering design, to the identification and destruction of enemy targets. The advantages of digital computers include speed, accuracy, and manpower savings. Often computers are able to take over routine jobs and release personnel for more important work that cannot be handled by a computer.

People and computers do not normally speak the same language. Methods of translating information into forms that are understandable and usable to both are necessary. Humans generally speak in words and numbers expressed in the decimal number system, while computers only understand coded electronic pulses that represent digital information.

In this chapter you will learn about number systems in general and about binary, octal, and hexadecimal (which we will refer to as hex) number systems specifically. Methods for converting numbers in the binary, octal, and hex systems to equivalent numbers in the decimal system (and vice versa) will also be described. You will see that these number systems can be easily converted to the electronic signals necessary for digital equipment.

#### 1.4 TYPESOF NUMBER SYSTEMS

Until now, you have probably used only one number system, the decimal system. You may also be familiar with the Roman numeral system, even though you seldom use it.

#### **1.4.1** The Decimal Number System

In this module you will be studying modern number systems. You should realize that these systems have certain things in common. These common terms will be defined using the decimal system as our base. Each term will be related to each number system as that number system is introduced.

Each of the number systems you will study is built around the following components: the UNIT, NUMBER, and BASE (RADIX).

#### **Unit and Number**

The terms *unit* and *number* when used with the decimal system are almost self-explanatory. By definition the unit is a single object; that is, an apple, a dollar, a day. A number is a symbol representing a unit or a quantity. The figures 0, 1, 2, and 3 through 9 are the symbols used in the decimal system. These symbols are called Arabic numerals or figures. Other symbols may be used for different number systems. For example, the symbols used with the Roman numeral system are letters - V is the symbol for 5, X for 10, M for 1,000, and so forth. We will use Arabic numerals and letters in the number system discussions in this chapter.

#### Base (Radix)

The base, or radix, of a number system tells you the number of symbols used in that system. The base of any system is always expressed in decimal numbers. The base, or radix, of the decimal system is 10. This means there are 10 symbols - 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9 - used in the system. A number system using three symbols - 0, 1, and 2 - would be base 3; four symbols would be base 4; and so forth. Remember to count the zero or the symbol used for zero when determining the number of symbols used in a number system.

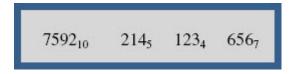

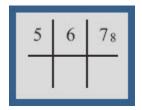

The base of a number system is indicated by a subscript (decimal number) following the value of the number. The following are examples of numerical values in different bases with the subscript to indicate the base:

You should notice the highest value symbol used in a number system is always one less than the base of the system. In base 10 the largest value symbol possible is 9; in base 5 it is 4; in base 3 it is 2.

#### Positional Notation and Zero

You must observe two principles when counting or writing quantities or numerical values. They are the POSITIONAL NOTATION and the ZERO principles.

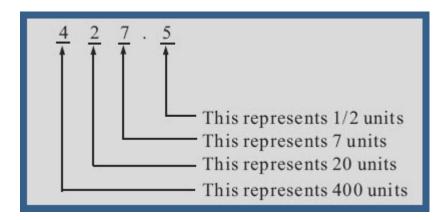

Positional notation is a system where the value of a number is defined not only by the symbol but by the symbol's position. Let's examine the decimal (base 10) value of 427.5. You know from experience that this value is four hundred twenty-seven and one-half. Now examine the position of each number:

If 427.5 is the quantity you wish to express, then each number must be in the position shown. If you exchange the positions of the 2 and the 7, then you change the value.

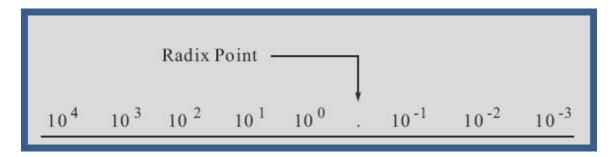

Each position in the positional notation system represents a power of the base, or radix. A POWER is the number of times a base is multiplied by itself. The power is written above and to the right of the base and is called an EXPONENT. Examine the following base 10 line graph:

Radix Point

$$10^{3} 10^{2} 10^{1} 10^{0} \cdot 10^{-1} 10^{-2} 10^{-3}$$

$$10^{3} = 10 \times 100, \text{ or } 1000$$

$$10^{2} = 10 \times 10, \text{ or } 100$$

$$10^{1} = 10 \times 1, \text{ or } 10$$

$$10^{0} = (\text{any number raised to the power of 0 equals 1})$$

$$10^{-1} = 1 + 10, \text{ or } .1$$

$$10^{-2} = 1 + 100. \text{ or } .01$$

$$10^{-3} = 1 + 1000, \text{ or } .001$$

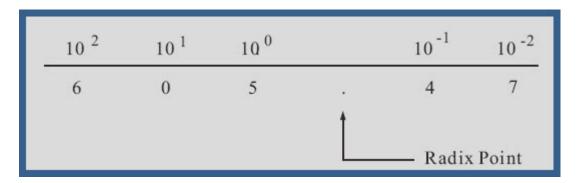

Now let's look at the value of the base 10 number 427.5 with the positional notation line graph:

Radix Point

$$\frac{10^{2} \quad 10^{1} \quad 10^{0} \quad \cdot \quad 10^{-1}}{4 \quad 2 \quad 7 \quad \cdot \quad 5}$$

$$10^{2} = 4 \times 100, \text{ or } 400$$

$$10^{1} = 2 \times 10, \text{ or } 20$$

$$10^{0} = 7 \times 1, \text{ or } 7$$

$$10^{-1} = 5 \times .1, \text{ or } .5$$

You can see that the power of the base is multiplied by the number in that position to determine the value for that position.

The following graph illustrates the progression of powers of 10:

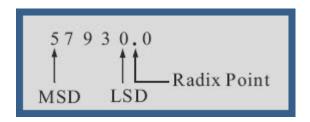

All numbers to the left of the decimal point are whole numbers, and all numbers to the right of the decimal point are fractional numbers. A whole number is a symbol that represents one, or more, complete objects, such as one apple or \$5. A fractional number is a symbol that represents a portion of an object, such as half of an apple (.5 apples) or a quarter of a dollar (\$0.25). A mixed number represents one, or more, complete objects, and some portion of an object, such as one and a half apples (1.5 apples). When you use any base other than the decimal system, the division between whole numbers and fractional numbers is referred to as the RADIX POINT. The decimal point is actually the radix point of the decimal system, but the term radix point is normally not used with the base 10 number system.

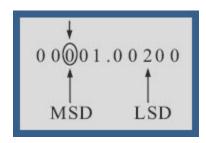

Just as important as positional notation is the use of the zero. The placement of the zero in a number can have quite an effect on the value being represented. Sometimes a position in a number does not have a value between 1 and 9. Consider how this would affect your next paycheck. If you were expecting a check for \$605.47, you wouldn't want it to be \$65.47. Leaving out the zero in this case means a difference of \$540.00. In the number 605.47, the zero indicates that there are no tens. If you place this value on a bar graph, you will see that there are no multiples of  $10^1$ .

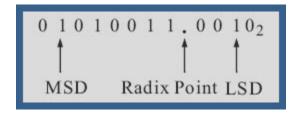

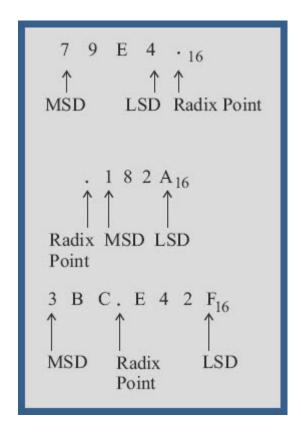

#### Most Significant Digit and Least Significant Digit (MSD and LSD)

Other important factors of number systems that you should recognize are the MOST SIGNIFICANT DIGIT (MSD) and the LEAST SIGNIFICANT DIGIT (LSD).

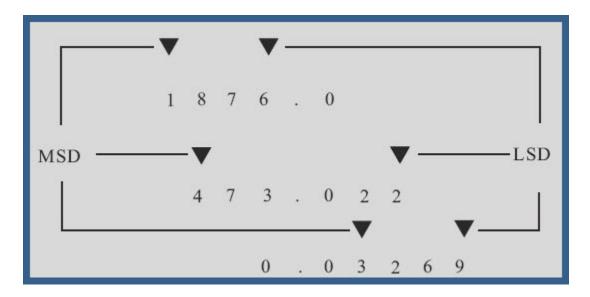

The MSD in a number is the digit that has the *greatest* effect on that number.

The LSD in a number is the digit that has the *least* effect on that number.

Look at the following examples:

You can easily see that a change in the MSD will increase or decrease the value of the number the greatest amount. Changes in the LSD will have the smallest effect on the value. The nonzero digit of a number that is the farthest LEFT is the MSD, and the nonzero digit farthest RIGHT is the LSD, as in the following example:

In a whole number the LSD will always be the digit immediately to the left of the radix point.

Q1. What term describes a single object?

Q2. A symbol that represents one or more objects is called a \_\_\_\_\_.

Q3. The symbols 0, 1, 2, and 3 through 9 are what type of numerals?

| <i>Q4</i> . | What does the base or radix of a number system tell you about the system? |

|-------------|---------------------------------------------------------------------------|

|             |                                                                           |

|             |                                                                           |

| Q5.         | How would you write one hundred seventy-three base 10?                    |

|             |                                                                           |

|             |                                                                           |

|             |                                                                           |

| <i>Q</i> 6. | What power of 10 is equal to 1,000? 100? 10? 1?                           |

|             |                                                                           |

|             |                                                                           |

| Q7.         | The decimal point of the base 10 number system is also known as the       |

|             |                                                                           |

|             |                                                                           |

| <i>Q</i> 8. | What is the MSD and LSD of the following numbers                          |

|             | (a) 420.                                                                  |

|             | (b) 1045.06                                                               |

|             | (c) 0.0024<br>(d) 247.0001                                                |

|             |                                                                           |

#### **Carry and Borrow Principles**

Soon after you learned how to count, you were taught how to add and subtract. At that time, you learned some concepts that you use almost everyday. Those concepts will be reviewed using the decimal system. They will also be applied to the other number systems you will study.

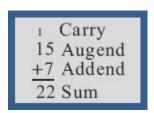

ADDITION-Addition is a form of counting in which one quantity is added to another. The following definitions identify the basic terms of addition:

AUGEND-The quantity to which an addend is added

ADDEND-A number to be added to a preceding number

SUM -The result of an addition (the sum of 5 and 7 is 12)

CARRY -A carry is produced when the sum of two or more digits in a vertical column equals or exceeds the base of the number system in use

How do we handle the carry; that is, the two-digit number generated when a carry is produced? The lower order digit becomes the sum of the column being added; the higher order digit (the carry) is added to the next higher order column. For example, let's add 15 and 7 in the decimal system:

Starting with the first column, we find the sum of 5 and 7 is 12. The 2 becomes the sum of the lower order column and the 1 (the carry) is added to the upper order column. The sum of the upper order column is 2. The sum of 15 and 7 is, therefore, 22.

The rules for addition are basically the same regardless of the number system being used. Each number system, because it has a different number of digits, will have a unique digit addition table. These addition tables will be described during the discussion of the adding process for each number system.

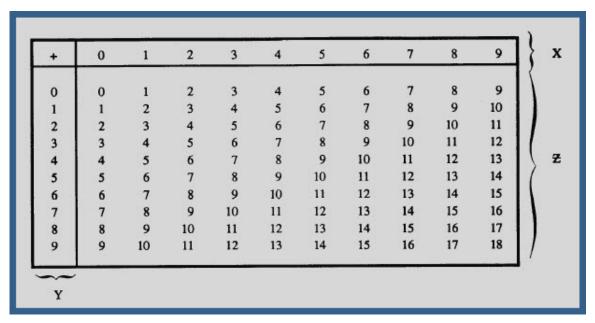

A decimal addition table is shown in table 1-1. The numbers in row X and column Y may represent either the addend or the augend. If the numbers in X represent the augend, then the numbers in Y must represent the addend and vice versa. The sum of X + Y is located at the point in array Z where the selected X row and Y column intersect.

**Table 1-1 Decimal Addition Table**

To add 5 and 7 using the table, first locate one number in the X row and the other in the Y column. The point in field Z where the row and column intersect is the sum. In this case the sum is 12.

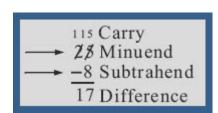

**SUBTRACTION**.-The following definitions identify the basic terms you will need to know to understand subtraction operations:

- SUBTRACT-To take away, as a part from the whole or one number from another

- MINUEND-The number from which another number is to be subtracted

- SUBTRAHEND-The quantity to be subtracted

- REMAINDER, or DIFFERENCE-That which is left after subtraction

- BORROW-To transfer a digit (equal to the base number) from the next higher order column for the purpose of subtraction.

Use the rules of subtraction and subtract 8 from 25. The form of this problem is probably familiar to you:

In addition,

$$X + Y = Z$$

In subtraction, the reverse is true; that is,

$$Z - Y = X$$

$$OR$$

$$Z - X = Y$$

Thus, in subtraction the minuend is always found in array Z and the subtrahend in either row X or column Y. If the subtrahend is in row X, then the remainder will be in column Y. Conversely, if the subtrahend is in column Y, then the difference will be in row X. For example, to subtract 8 from 15, find 8 in either the X row or Y column. Find where this row or column intersects with a value of 15 for Z; then move to the remaining row or column to find the difference.

#### 1.4.2 The Binary Number System

The simplest possible number system is the BINARY, or base 2, system. You will be able to use the information just covered about the decimal system to easily relate the same terms to the binary system.

#### **Unit and Number**

The base, or radix-you should remember from our decimal section-is the number of symbols used in the number system. Since this is the base 2 system, only two symbols, 0 and 1, are used. The base is indicated by a subscript, as shown in the following example:

When you are working with the decimal system, you normally don't use the subscript. Now that you will be working with number systems other than the decimal system, it is important that you use the subscript so that you are sure of the system being referred to. Consider the following two numbers:

With no subscript you would assume both values were the same. If you add subscripts to indicate their base system, as shown below, then their values are quite different:

The base ten number  $11_{10}$  is eleven, but the base two number  $11_2$  is only equal to three in base ten. There will be occasions when more than one number system will be discussed at the same time, so you MUST use the proper Subscript.

$$\frac{2^4 \ 2^3 \ 2^2 \ 2^1 \ 2^0 . \ 2^{-1} \ 2^{-2} \ 2^{-3}}{2^4 \text{ is equal to } 2 \times 2 \times 2 \times 2, \text{ or } 16_{10}}$$

$$2^3 \text{ is equal to } 2 \times 2 \times 2, \text{ or } 8_{10}$$

$$2^2 \text{ is equal to } 2 \times 2, \text{ or } 4_{10}$$

$$2^1 \text{ is equal to } 2 \times 1, \text{ or } 2_{10}$$

$$2^0 \text{ is equal to } 1_{10}$$

$$2^{-1} \text{ is equal to } 1/2, \text{ or } .5_{10}$$

$$2^{-2} \text{ is equal to } 1/4, \text{ or } .25_{10}$$

$$2^{-3} \text{ is equal to } 1/8, \text{ or } .125_{10}$$

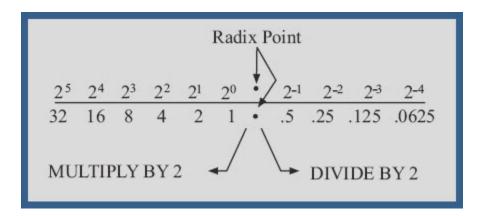

All numbers or values to the left of the radix point are whole numbers, and all numbers to the right of the radix point are fractional numbers.

Let's look at the binary number 101.1 on a bar graph:

Working from the radix point to the right and left, you can determine the decimal equivalent:

$$1 \times 2^{-1} = .5_{10}$$

$$1 \times 2^{0} = 1.0_{10}$$

$$1 \times 2^{1} = 0.0_{10}$$

$$1 \times 2^{2} = 4.0_{10}$$

$$5.5_{10}$$

Table 1-2 provides a comparison of decimal and binary numbers. Notice that each time the total number of binary symbol positions increase, the binary number indicates the next higher power of 2. By this example, you can also see that more symbol positions are needed in the binary system to represent the equivalent value in the decimal system.

|                 | DECIMAL          | BINARY     |                |

|-----------------|------------------|------------|----------------|

| <u>10</u> 0     | 0                | 0          | 20             |

|                 | 1                | 1          |                |

|                 | 2                | 10         | 2 <sup>1</sup> |

|                 | 2<br>3<br>4<br>5 | 11         | 2 <sup>2</sup> |

|                 | 4                | 100        | 22             |

|                 | 6                | 101        |                |

|                 | 7                | 110<br>111 |                |

|                 | 8                | 1000       | 23             |

|                 | 9                | 1001       |                |

| 10 <sup>1</sup> | 10               | 1010       |                |

|                 | 11               | 1011       |                |

|                 | 12               | 1100       |                |

|                 | 13               | 1101       |                |

|                 | 14               | 1110       |                |

|                 | 15               | 1111       | 2 <sup>4</sup> |

|                 | 16               | 10000      | 2              |

|                 | 17<br>18         | 10001      |                |

|                 | 19               | 10010      |                |

|                 | 20               | 10100      |                |

**Table 1-2 Decimal and Binary Comparison**

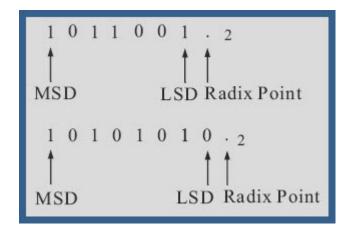

#### MSD and LSD

When you're determining the MSD and LSD for binary numbers, use the same guidelines you used with the decimal system. As you read from left to right, the first nonzero digit you encounter is the MSD, and the last nonzero digit is the LSD.

If the number is a whole number, then the first digit to the left of the radix point is the LSD.

Here, as in the decimal system, the MSD is the digit that will have the most effect on the number; the LSD is the digit that will have the least effect on the number.

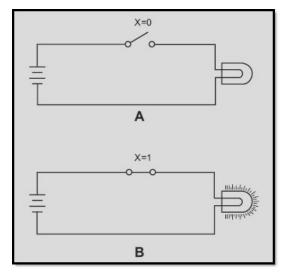

The two numerals of the binary system (1 and 0) can easily be represented by many electrical or electronic devices. For example, 1<sub>2</sub> may be indicated when a device is active (on), and 0<sub>2</sub> may be indicated when a device is nonactive (off).

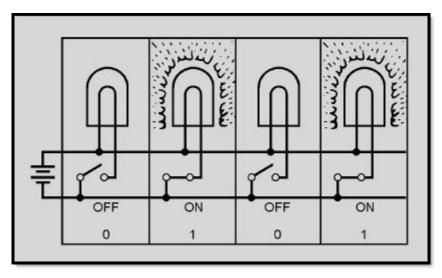

Figure 1-1 Binary Example

Look at the preceding figure. It illustrates a very simple binary counting device. Notice that  $1_2$  is indicated by a lighted lamp and  $0_2$  is indicated by an unlighted lamp. The reverse will work equally well. The unlighted state of the lamp can be used to represent a binary 1 condition, and the lighted state can represent the binary 0 condition. Both methods are used in digital computer applications. Many other devices are used to represent binary conditions. They include switches, relays, diodes, transistors, and integrated circuits (ICs).

#### **Addition of Binary Numbers**

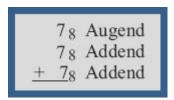

Addition of binary numbers is basically the same as addition of decimal numbers. Each system has an augend, an addend, a sum, and carries. The following example will refresh your memory:

Since only two symbols, 0 and 1, are used with the binary system, only four combinations of addition are possible.

The sum of each of the first three combinations is obvious:

$$0 + 0 = 0_2$$

$0 + 1 = 1_2$

$1 + 0 = 1_2$

The fourth combination presents a different situation. The sum of 1 and 1 in any other number system is 2, but the numeral 2 does not exist in the binary system. Therefore, the sum of  $1_2$  and  $1_2$  is  $10_2$  (spoken as one zero base two), which is equal to  $2_{10}$ .

Study the following examples using the four combinations mentioned above:

When a carry is produced, it is noted in the column of the next higher value or in the column immediately to the left of the one that produced the carry.

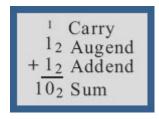

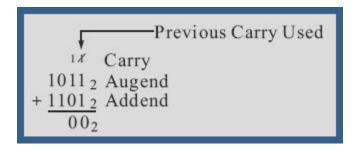

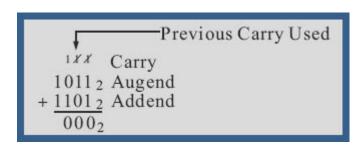

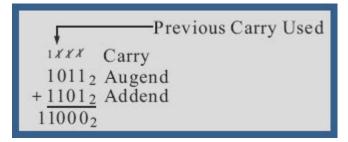

Example: Add 1011<sub>2</sub> and 1101<sub>2</sub>.

Solution: Write out the problem as shown:

As we noted previously, the sum of 1 and 1 is 2, which cannot be expressed as a single digit in the binary system. Therefore, the sum of 1 and 1 produces a carry:

The following steps, with the carry indicated, show the completion of the addition:

When the carry is added, it is marked through to prevent adding it twice.

In the final step the remaining carry is brought down to the sum.

In the following example you will see that more than one carry may be produced by a single column. This is something that does not occur in the decimal system.

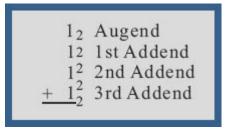

Example: Add 1<sub>2</sub>, 1<sub>2</sub>, 1<sub>2</sub>, and 1<sub>2</sub>

The sum of the augend and the first addend is 0 with a carry. The sum of the second and third addends is also 0 with a carry. At this point the solution resembles the following example:

1 Carry

1 Carry

1 Augend

12 1st Addend

12 2nd Addend

$$+ 1_2^2 3rd Addend$$

02

The sum of the carries is 0 with a carry, so the sum of the problem is as follows:

1 Carry

11 Carry

12 Augend

12 1st Addend

12 2nd Addend

$$\frac{1^2}{100_2}$$

3rd Addend

The same situation occurs in the following example:

Add 100<sub>2</sub>, 101<sub>2</sub>, and 111<sub>2</sub>

As in the previous example, the sum of the four 1s is 0 with two carries, and the sum of the two carries is 0 with one carry. The final solution will look like this:

In the addition of binary numbers, you should remember the following binary addition rules:

Rule 1:

$$0_2 + 0_2 = 0_2$$

Rule 2:

$$1_2 + 0_2 = 1_2$$

Rule 3:

$$0_2 + 1_2 = 1_2$$

Rule 4:

$$1_2 + 1_2 = 10_2$$

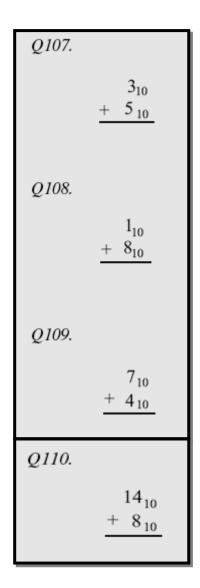

Now practice what you've learned by solving the following problems:

### **Subtraction of Binary Numbers**

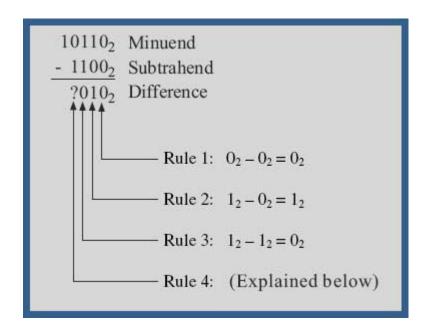

Now that you are familiar with the addition of binary numbers, subtraction will be easy. The following are the four rules that you must observe when subtracting:

Rule 1:

$$0_2 - 0_2 = 0_2$$

Rule 2:  $1_2 - 0_2 = 1_2$

Rule 3:  $1_2 - 1_2 = 0_2$

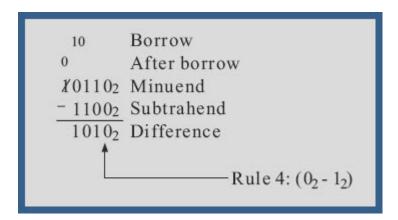

Rule 4:  $0_2 - 1_2 = 1_2$  with a borrow

The following example  $(10110_2 - 1100_2)$  demonstrates the four rules of binary subtraction:

Rule 4 presents a different situation because you cannot subtract 1 from 0. Since you cannot subtract 1 from 0 and have a positive difference, you must borrow the 1 from the next higher order column of the minuend. The borrow may be indicated as shown below:

Now observe the following method of borrowing across more than one column in the example,  $1000_2$  -  $1_2$ :

1 1 Borrow

0 ががい After borrow (base 2)

1000<sub>2</sub> Minuend

- 1<sub>2</sub> Subtrahend

- 0111<sub>2</sub> Difference

Let's practice some subtraction by solving the following problems:

Q15. Subtract:

$$1100 l_2 - 100 l_2$$

Q16. Subtract:

$$-\frac{10101_2}{1010_2}$$

Q17. Subtract:

$$-\frac{11111_2}{10_2}$$

#### **Complementary Subtraction**

If you do any work with computers, you will soon find out that most digital systems cannot subtract-they can only add. You are going to need a method of adding that gives the results of subtraction. Does that sound confusing? Really, it is quite simple. A COMPLEMENT is used for our subtractions. A complement is something used to complete something else.

In most number systems you will find two types of complements. The first is the amount necessary to complete a number up to the highest number in the number system. In the decimal system, this would be the difference between a given number and all 9s. This is called the nines complement or the radix-1 or R's-1 complement. As an example, the nines complement of 254 is 999 minus 254, or 745.

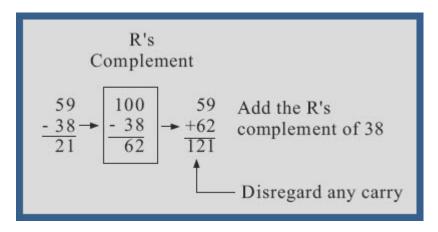

The second type of complement is the difference between a number and the next higher power of the number base. As an example, the next higher power of 10 above 999 is 1,000. The difference between 1,000 and 254 is 746. This is called the tens complement in the decimal number system. It is also called the radix or R's complement. We will use complements to subtract. Let's look at the *magic* of this process. There are three important points we should mention before we start: (1) Never complement the minuend in a problem, (2) always disregard any carry beyond the number of positions of the largest of the original numbers, and (3) add the R's complement of the original subtrahend to the original minuend. This will have the same effect as subtracting the original number. Let's look at a base ten example in which we subtract 38 from 59:

Now let's look at the number system that most computers use, the binary system. Just as the decimal system, had the nines (R's-1) and tens (R's) complement, the binary system has two types of complement methods. These two types are the ones (R's-1) complement and the twos (R's) complement. The binary system R's-1 complement is the difference between the binary number and all 1s. The R's complement is the difference between the binary number and the next higher power of 2.

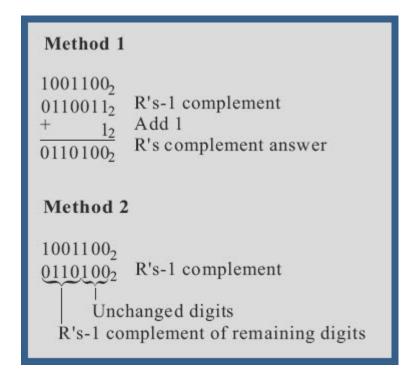

Let's look at a quick and easy way to form the R's-1 complement. To do this, change each 1 in the original number to 0 and each 0 in the original number to 1 as has been done in the example below.

1011011<sub>2</sub> 100100<sub>2</sub> R's-1 complement

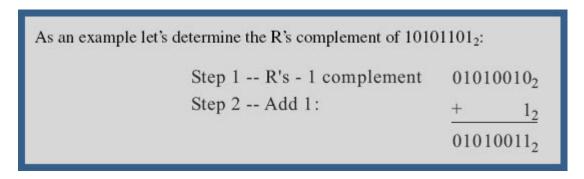

There are two methods of achieving the R's complement. In the first method we perform the R's-1 complement and then add 1. This is much easier than subtracting the original number from the next higher power of 2. If you had subtracted, you would have had to borrow.

Saying it another way, to reach the R's complement of any binary number, change all 1s to 0s and all 0s to 1s, and then add 1.

As an example let's determine the R's complement of 10101101<sub>2</sub>:

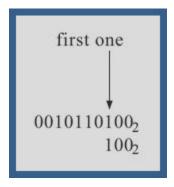

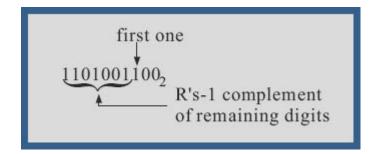

The second method of obtaining the R's complement will be demonstrated on the binary number 00101101100<sub>2</sub>.

Step 1—Start with the LSD, working to the MSD, writing the digits as they are up to and including the first one.

Step 2—Now R's-1 complement the remaining digits:

Now let's R's complement the same number using both methods:

Now let's do some subtracting by using the R's complement method. We will go through the subtraction of  $3_{10}$  from  $9_{10}$  (00112 from  $1001_2$ ):

$$\frac{9_{10}}{-3_{10}}$$

$\frac{1001_{2}}{-0011_{2}}$  Minuend Subtrahend

Step 1-Leave the minuend alone:

1001<sub>2</sub> remains 1001<sub>2</sub>

Step 2—Using either method, R's complement the subtrahend:

1101<sub>2</sub> R's complement of subtrahend

Step 3-Add the R's complement found in step 2 to the minuend of the original problem:

Step 4—Remember to discard any carry beyond the size of the original number. Our original problem had four digits, so we discard the carry that expanded the difference to five digits. This carry we disregard is significant to the computer. It indicates that the difference is positive. Because we have a carry, we can read the difference directly without any further computations. Let's check our answer:

$$\frac{1001_2 = 9_{10}}{-0011_2} = \frac{-3_{10}}{6_{10}}$$

$$\frac{10110_2}{6_{10}} = \frac{-3_{10}}{6_{10}}$$

Discard

If we do *not* have a carry, it indicates the difference is a negative number. In that case, the difference must be R's complemented to produce the correct answer.

Let's look at an example that will explain this for you.

Subtract  $9_{10}$  from  $5_{10}$  (1001<sub>2</sub> from 0101<sub>2</sub>):

Step 1—Leave the minuend alone:

0101<sub>2</sub> remains 0101<sub>2</sub>

Step 2—R's complement the subtrahend:

01112 R's complement of subtrahend

Step 3—Add the R's complement found in step 2 to the minuend of the original problem:

$$\begin{array}{c} 0101_2 & \text{Original minuend} \\ +0111_2 & \text{Twos complement} \\ \hline 1100_2 & \text{Difference of original problem} \end{array}$$

Step 4—We do *not* have a carry; and this tells us, and any computer, that our difference (answer) is negative. With no carry, we must R's complement the difference in step 3. We will then have arrived at the answer (difference) to our original problem. Let's do this R's complement step and then check our answer:

0100<sub>2</sub> R's complement of difference in step 3

Remember, we had no carry in step 3. That showed us our answer was going to be negative. Make sure you indicate the difference is negative. Let's check the answer to our problem:

$$0101_2 = 5_{10}$$

$$-1001_2 = -9_{10}$$

$$-0100_2 = -4_{10}$$

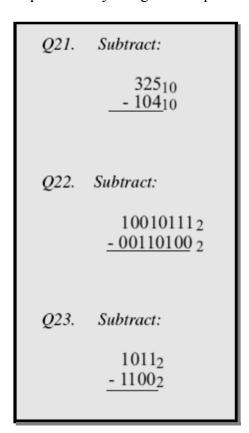

Try solving a few subtraction problems by using the complement method:

#### 1.4.3 Octal Number System

The octal, or base 8, number system is a common system used with computers. Because of its relationship with the binary system, it is useful in programming some types of computers.

Look closely at the comparison of binary and octal number systems in table 1-3. You can see that one octal digit is the equivalent value of three binary digits. The following examples of the conversion of octal 225<sub>8</sub> to binary and back again further illustrate this comparison:

| Octa | l to bi | nary | Binary to Octal |     |      |  |  |  |  |

|------|---------|------|-----------------|-----|------|--|--|--|--|

| 2    | 2       | 58   | 010             | 010 | 1012 |  |  |  |  |

| 010  | 010     | 1012 | 2               | 2   | 58   |  |  |  |  |

|                      | BINARY         | OCTAL                 |                |

|----------------------|----------------|-----------------------|----------------|

| 20                   | 0              | 0                     | 80             |

| 22                   | 1              | 1                     |                |

| 21                   | 10             | 2                     |                |

| $\frac{2^1}{2^2}$    | 11             | 2<br>3<br>4<br>5<br>6 |                |

| 22                   | 100            | 4                     |                |

|                      | 101            | 5                     |                |

|                      | 110            |                       |                |

| 2                    | 111            | 7                     | -1             |

| <u>2<sup>3</sup></u> | 1000           | _10                   | 8 <sup>1</sup> |

|                      | 1001           | 11                    |                |

|                      | 1010           | 12                    |                |

|                      | 1011           | 13                    |                |

|                      | 1100           | 14                    |                |

|                      | 1101           | 15                    |                |

|                      | 1110           | 16                    |                |

| -4                   | 1111           | 17                    |                |

| 24                   | 10000          | 20                    |                |

|                      | 10001<br>10010 | 21                    |                |

|                      | 10010          | 22                    |                |

|                      | 10100          | 23<br>24              |                |

|                      | 10100          | 25                    |                |

|                      | 10101          | 26                    |                |

|                      | 10111          | 27                    |                |

|                      | 11000          | 30                    |                |

|                      | 11000          | 30                    |                |

**Table 1-3 Binary and Octal Comparison**

#### **Unit and Number**

The terms that you learned in the decimal and binary sections are also used with the octal system. The unit remains a single object, and the number is still a symbol used to represent one or more units.

#### Base (Radix)

As with the other systems, the radix, or base, is the number of symbols used in the system. The octal system uses eight symbols - 0 through 7. The base, or radix, is indicated by the subscript 8.

#### **Positional Notation**

The octal number system is a positional notation number system. Just as the decimal system uses powers of 10 and the binary system uses powers of 2, the octal system uses power of 8 to determine the value of a number's position. The following bar graph shows the positions and the power of the base:

$$8^3 8^2 8^1 8^0 \bullet 8^{-1} 8^{-2} 8^{-3}$$

Remember, that the power, or exponent, indicates the number of times the base is multiplied by itself. The value of this multiplication is expressed in base 10 as shown below:

$$8^{3} = 8 \times 8 \times 8, \text{ or } 512_{10}$$

$$8^{2} = 8 \times 8, \text{ or } 64_{10}$$

$$8^{1} = 8_{10}$$

$$8^{0} = 1_{10}$$

$$8^{-1} = \frac{1}{8}, \text{ or } .125_{10}$$

$$8^{-2} = \frac{1}{8 \times 8}, \text{ or } \frac{1}{64}, \text{ or } .015625_{10}$$

$$8^{-3} = \frac{1}{8 \times 8 \times 8}, \text{ or } \frac{1}{512}, \text{ or } .0019531_{10}$$

All numbers to the left of the radix point are whole numbers, and those to the right are fractional numbers.

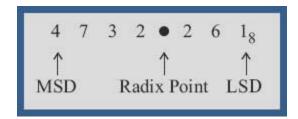

#### MSD and LSD

When determining the most and least significant digits in an octal number, use the same rules that you used with the other number systems. The digit farthest to the left of the radix point is the MSD, and the one farthest right of the radix point is the LSD.

Example:

If the number is a whole number, the MSD is the nonzero digit farthest to the left of the radix point and the LSD is the digit immediately to the left of the radix point. Conversely, if the number is a fraction only, the nonzero digit closest to the radix point is the MSD and the LSD is the nonzero digit farthest to the right of the radix point.

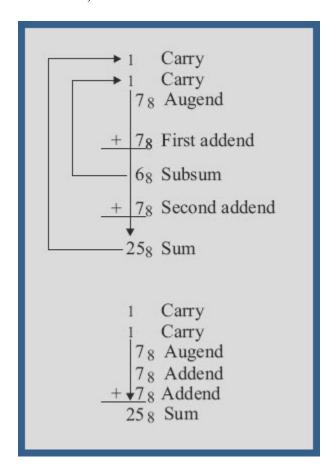

#### **Addition of Octal Numbers**

The addition of octal numbers is not difficult provided you remember that anytime the sum of two digits exceeds 7, a carry is produced. Compare the two examples shown below:

$$\begin{array}{c|cccc}

48 & 48 \\

+28 & +48 \\

\hline

68 & 108

\end{array}$$

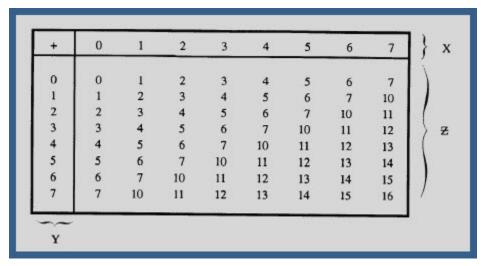

The octal addition table in table 1-4 will be of benefit to you until you are accustomed to adding octal numbers. To use the table, simply follow the directions used in this example:

Add: 6<sub>8</sub> and 5<sub>8</sub>

**Table 1-4 Octal Addition Table**

Locate the 6 in the X column of the figure. Next locate the 5 in the Y column. The point in area Z where these two columns intersect is the sum.

$$\frac{68}{138}$$

(spoken, "one three, base eight")

If you use the concepts of addition you have already learned, you are ready to add octal numbers.

Work through the solutions to the following problems:

As was mentioned earlier in this section, each time the sum of a column of numbers exceeds 7, a carry is produced. More than one carry may be produced if there are three or more numbers to be added, as in this example:

The sum of the augend and the first addend is 68 with a carry. The sum of 68 and the second addend is 58 with a carry. You should write down the 58 and add the two carries and bring them down to the sum, as shown below:

Now let's try some practice problems:

$$\frac{228}{+368}$$

$$^{13255_8}_{+\underline{7031}_8}$$

$$\begin{array}{r}

3_8 \\

5_8 \\

2_8 \\

6_8 \\

+ 4_8

\end{array}$$

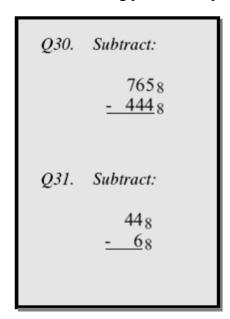

#### **Subtraction of Octal Numbers**

The subtraction of octal numbers follows the same rules as the subtraction of numbers in any other number system. The only variation is in the quantity of the borrow. In the decimal system, you had to borrow a group of  $10_{10}$ . In the binary system, you borrowed a group of  $2_{10}$ . In the octal system you will borrow a group of  $8_{10}$ .

Consider the subtraction of 1 from 10 in decimal, binary, and octal number systems:

In each example, you cannot subtract 1 from 0 and have a positive difference. You must use a borrow from the next column of numbers. Let's examine the above problems and show the borrow as a *decimal* quantity for clarity:

When you use the borrow, the column you borrow from is reduced by 1, and the amount of the borrow is added to the column of the minuend being subtracted. The following examples show this procedure:

In the octal example 78 cannot be subtracted from 68, so you must borrow from the 4. Reduce the 4 by 1 and add 108 (the borrow) to the 68 in the minuend. By subtracting 78 from 168, you get a difference of 78. Write this number in the difference line and bring down the 3. You may need to refer to table 1-4, the octal addition table, until you are familiar with octal numbers. To use the table for subtraction, follow these directions. Locate the subtrahend in column Y. Now find where this line intersects with the minuend in area Z. The remainder, or difference, will be in row X directly above this point.

Do the following problems to practice your octal subtraction:

Check your answers by adding the subtrahend and difference for each problem.

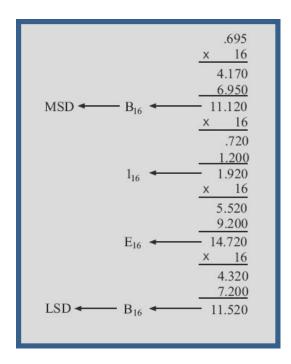

#### 1.4.4 Hexadecimal (HEX) Number System

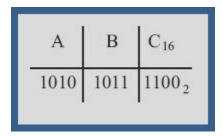

The hex number system is a more complex system in use with computers. The name is derived from the fact the system uses 16 symbols. It is beneficial in computer programming because of its relationship to the binary system. Since 16 in the decimal system is the fourth power of 2 (or 2<sup>4</sup>); one hex digit has a value equal to four binary digits. Table 1-5 shows the relationship between the two systems.

|                                  | BINARY       | OCTAL                                     |                                         |

|----------------------------------|--------------|-------------------------------------------|-----------------------------------------|

| 20                               | 0            | 0                                         | 16 <sup>0</sup>                         |

|                                  | 0            | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | *************************************** |

| 2 <sup>1</sup><br>2 <sup>2</sup> | 10           | 2                                         |                                         |

|                                  | 11           | 3                                         |                                         |

| 24                               | 100          | 4                                         |                                         |

|                                  | 101          | 5                                         |                                         |

|                                  | 110          | 6                                         |                                         |

| -3                               | 111          | 7                                         |                                         |

| 23                               | 1000         | 8                                         |                                         |

|                                  | 1001         |                                           |                                         |

|                                  | 1010         | A                                         |                                         |

|                                  | 1011         | В                                         |                                         |

|                                  | 1100         | C                                         |                                         |

|                                  | 1101         | D                                         |                                         |

|                                  | 1110<br>1111 | E                                         |                                         |

| 24                               | 10000        | F                                         | 1/1                                     |

|                                  | 10000        | 10                                        | 16 <sup>1</sup>                         |

|                                  | 10001        | 12                                        |                                         |

|                                  | 10010        | 13                                        |                                         |

|                                  | 10100        | 14                                        |                                         |

|                                  | 10101        | 15                                        |                                         |

|                                  | 10110        | 16                                        |                                         |

|                                  | 10111        | 17                                        |                                         |

|                                  | 11000        | 18                                        |                                         |

|                                  | 11001        | 19                                        |                                         |

|                                  | 11010        | 1A                                        |                                         |

|                                  | 11011        | 1B                                        |                                         |

|                                  | 11100        | 1C                                        |                                         |

**Table 1-5 Binary and Hexadecimal Comparison**

#### **Unit and Number**

As in each of the previous number systems, a unit stands for a single object. A number in the hex system is the symbol used to represent a unit or quantity. The Arabic numerals 0 through 9 are used along with the first six letters of the alphabet. You have probably used letters in math problems to represent unknown quantities, but in the hex system A, B, C, D, E, and F, each have a definite value as shown below:

$$A_{16} = 10_{10}$$

$$B_{16} = 11_{10}$$

$$C_{16} = 12_{10}$$

$$D_{16} = 13_{10}$$

$$E_{16} = 14_{10}$$

$$F_{16} = 15_{10}$$

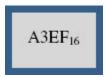

#### Base (Radix)

The base, or radix, of this system is 16, which represents the number of symbols used in the system. A quantity expressed in hex will be annotated by the subscript 16, as shown below:

#### **Positional Notation**

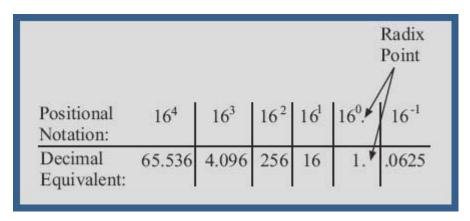

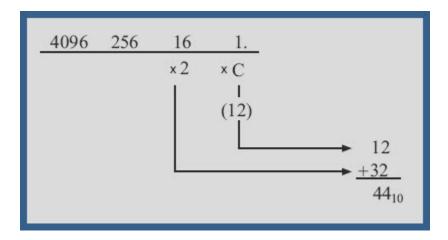

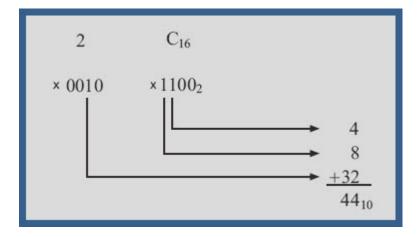

Like the binary, octal, and decimal systems, the hex system is a positional notation system. Powers of 16 are used for the positional values of a number. The following bar graph shows the positions:

$$16^3 16^2 16^1 16^0 \bullet 16^{-1} 16^{-2} 16^{-3}$$

Multiplying the base times itself the number of times indicated by the exponent will show the equivalent decimal value:

$$16^{3} = 16 \times 16 \times 16, \text{ or } 4096_{10}$$

$$16^{3} = 16 \times 16, \text{ or } 256_{10}$$

$$16^{1} = 16_{10}$$

$$16^{0} = 1_{10}$$

$$16^{-1} = \frac{1}{16}, \text{ or } .0625_{10}$$

$$16^{-2} = \frac{1}{16 \times 16}, \text{ or } .0039062_{10}$$

$$16^{-3} = \frac{1}{16 \times 16 \times 16}, \text{ or } .0002441_{10}$$

You can see from the positional values that usually fewer symbol positions are required to express a number in hex than in decimal. The following example shows this comparison:

625<sub>16</sub> is equal to 1573<sub>10</sub>

#### MSD and LSD

The most significant and least significant digits will be determined in the same manner as the other number systems. The following examples show the MSD and LSD of whole, fractional, and mixed hex numbers:

#### **Addition of Hex Numbers**

The addition of hex numbers may seem intimidating at first glance, but it is no different than addition in any other number system. The same rules apply. Certain combinations of symbols produce a carry while others do not. Some numerals combine to produce a sum represented by a letter. After a little practice you will be as confident adding hex numbers as you are adding decimal numbers.

Study the hex addition table in table 1-6. Using the table, add 7 and 7. Locate the number 7 in both columns X and Y. The point in area Z where these two columns intersect is the sum; in this case 7 + 7 = E. As long as the sum of two numbers is  $15_{10}$  or less, only one symbol is used for the sum. A carry will be produced when the sum of two numbers is  $16_{10}$  or greater, as in the following examples:

| + | 0 | 1  | 2  | 3    | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | Е  | F  |   |

|---|---|----|----|------|----|----|----|----|----|----|----|----|----|----|----|----|---|

| 0 | 0 | 1  | 2  | 3    | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F  | 1 |

| 1 | 1 | 2  | 3  | 4    | 5  | 6  | 7  | 8  | 9  | Α  | В  | C  | D  | E  | F  | 10 | 1 |

| 2 | 2 | 3  | 4  | 5    | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F  | 10 | 11 |   |

| 3 | 3 | 4  | 5  | 6    | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F  | 10 | 11 | 12 |   |

| 4 | 4 | 5  | 6  | 7    | 8  | 9  | Α  | В  | С  | D  | E  | F  | 10 | 11 | 12 | 13 |   |

| 5 | 5 | 6  | 7  | 8    | 9  | Α  | В  | С  | D  | E  | F  | 10 | 11 | 12 | 13 | 14 |   |

| 6 | 6 | 7  | 8  | 9    | Α  | В  | С  | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 |   |

| 7 | 7 | 8  | 9  | Α    | В  | С  | D  | Е  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 1 |

| 8 | 8 | 9  | Α  | В    | С  | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |   |

| 9 | 9 | Α  | В  | С    | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |   |

| A | Α | В  | С  | D    | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1 |

| В | В | С  | D  | E    | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1 |

| c | С | D  | E  | F    | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1 |

| D | D | E  | F  | 10   | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1 |

| E | Е | F  | 10 | 11   | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1D |   |

| F | F | 10 | 11 | 12   | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1D | 1E |   |

| ~ |   |    |    | - 10 |    |    |    |    |    |    |    |    |    |    |    |    |   |

**Table 1-6 Hexadecimal Addition Table**

Use the addition table and follow the solution of the following problems:

In this example each column is straight addition with no carry.

Now add the addend ( $784_{16}$ ) and the sum (BDA<sub>16</sub>) of the previous problem:

$$\begin{array}{c|cccc}

1 & 1 & Carry \\

784_{16} & Augend \\

+ & & & & & & \\

\hline

1 & 3 & 5 & E_{16} & Sum

\end{array}$$

Here the sum of 4 and A is E. Adding 8 and D is  $15_{16}$ ; write down 5 and carry a 1. Add the first carry to the 7 in the next column and add the sum, 8, to B. The result is  $13_{16}$ ; write down 3 and carry a 1. Since only the last carry is left to add, bring it down to complete the problem.

Now observe the procedures for a more complex addition problem. You may find it easier to add the Arabic numerals in each column first:

The sum of 4, E, 1, and 3 in the first column is  $16_{16}$ . Write down the 6 and the carry. In the second column, 1, 1, 9, and 7 equals  $12_{16}$ . Write the carry over the next column. Add B and 2 - the sum is D. Write this in the sum line. Now add the final column, 1, 1, 5, and C. The sum is  $13_{16}$ . Write down the carry; then add 3 and B - the sum is E. Write down the E and bring down the final carry to complete the problem.

Now solve the following addition problems:

Q36. Add:

Q37. Add:

Q38. Add:

Q39. Add:

Q40. Add:

Q41. Add:

#### **Subtraction of Hex Numbers**

The subtraction of hex numbers looks more difficult than it really is. In the preceding sections you learned all the rules for subtraction. Now you need only to apply those rules to a new number system. The symbols may be different and the amount of the borrow is different, but the rules remain the same.

Use the hex addition table (table 1-6) to follow the solution of the following problems:

Working from left to right, first locate the subtrahend (2) in column Y. Follow this line across area Z until you reach C. The difference is located in column X directly above the C - in this case A. Use this same procedure to reach the solution:

Now examine the following solutions:

In the previous example, when F was subtracted from 1E, a borrow was used. Since you cannot subtract F from E and have a positive difference, a borrow of  $10_{16}$  was taken from the next higher value column. The borrow was added to E, and the higher value column was reduced by 1.

The following example shows the use of the borrow in a more difficult problem:

In this first step, B cannot be subtracted from 7, so you take a borrow of  $10_{16}$  from the next higher value column. Add the borrow to the 7 in the minuend; then subtract ( $17_{16}$  minus  $B_{16}$  equals  $C_{16}$ ). Reduce the number from which the borrow was taken (3) by 1.

To subtract  $4_{16}$  from  $2_{16}$  also requires a borrow, as shown below:

Borrow  $10_{16}$  from the A and reduce the minuend by 1. Add the borrow to the 2 and subtract  $4_{16}$  from  $12_{16}$ . The difference is E.

When solved the problem looks like this:

```

10 10 10 Borrow (Base 16)

3 9 2 Minuend reduced by 1

4 X Z 7 16 Minuend

- 2 C 4 B 16 Subtrahend

1 D E C 16 Difference

```

Remember that the borrow is  $10_{16}$  not  $10_{10}$ .

There may be times when you need to borrow from a column that has a 0 in the minuend. In that case, you borrow from the next highest value column, which will provide you with a value in the 0 column that you can borrow from.

To subtract A from 7, you must borrow. To borrow you must first borrow from the 2. The 0 becomes  $10_{16}$ , which can give up a borrow. Reduce the  $10_{16}$  by 1 to provide a borrow for the 7. Reducing  $10_{16}$  by 1 equals F. Subtracting  $A_{16}$  from  $17_{16}$  gives you  $D_{16}$ . Bring down the 1 and F for a difference of  $1FD_{16}$ .

Now let's practice what we've learned by solving the following hex subtraction problems:

#### 1.5 CONVERSION OF BASES

We mentioned in the introduction to this chapter that digital computers operate on electrical pulses. These pulses or the absence of, are easily represented by binary numbers. A pulse can represent a binary 1, and the lack of a pulse can represent a binary 0 or vice versa.

The sections of this chapter that discussed octal and hex numbers both mentioned that their number systems were beneficial to programmers. You will see later in this section that octal and hex numbers are easily converted to binary numbers and vice versa..

If you are going to work with computers, there will be many times when it will be necessary to convert decimal numbers to binary, octal, and hex numbers. You will also have to be able to convert binary, octal, and hex numbers to decimal numbers. Converting each number system to each of the others will be explained. This will prepare you for converting from any base to any other base when needed.

#### 1.6 DECIMAL CONVERSION

Some computer systems have the capability to convert decimal numbers to binary numbers. They do this by using additional circuitry. Many of these systems require that the decimal numbers be converted to another form before entry.

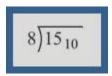

#### 1.6.1 Decimal to Binary

Conversion of a decimal number to any other base is accomplished by dividing the decimal number by the radix of the system you are converting to. The following definitions identify the basic terms used in division:

- DIVIDEND-The number to be divided

- DIVISOR-The number by which a dividend is divided

- QUOTIENT-The number resulting from the division of one number by another

- REMAINDER-The final undivided part after division that is less or of a lower degree than the divisor.

To convert a base 10 whole number to its binary equivalent, first set up the problem for division:

Step 1—Divide the base 10 number by the radix (2) of the binary system and extract the remainder (this becomes the binary number's LSD).

Divisor

$$2 ) 5_{10}$$

Quotient  $\frac{4}{1}$  Remainder  $\longrightarrow 1$

Step 2—Continue the division by dividing the quotient of step 1 by the radix (2 x 2).

$$\begin{array}{cc}

\frac{1}{2)2} & \text{(Quotient from step 1)} \\

\frac{2}{0} & \text{Remainder} \longrightarrow 0

\end{array}$$

Step 3—Continue dividing quotients by the radix until the quotient becomes smaller that the divisor; then do one more division. The remainder is our MSD.

$$\begin{array}{c}

0 \\

2)1 \\

0 \\

\hline

1

\end{array}$$

(Quotient from step 2)

Remainder  $\longrightarrow$  1

The remainder in step 1 is our LSD. Now rewrite the solution, and you will see that  $5_{10}$  equals  $101_2$ . Now follow the conversion of  $23_{10}$  to binary:

Step 1—Set up the problem for division:

Step 2—Divide the number and extract the remainder:

$$\frac{2}{03}$$

$$\frac{2}{03}$$

$$\frac{2}{1}$$

Remainder  $\longrightarrow 1$  (LSD)

$$\frac{5}{2)11}$$

(Quotient from previous step)

$$\frac{10}{1}$$

Remainder  $\longrightarrow 1$

$$\frac{2}{2)5}$$

(Quotient from previous step)

$$\frac{4}{1}$$

Remainder  $\longrightarrow 1$

$$\frac{1}{2)2}$$

(Quotient from previous step)

$$\frac{2}{0}$$

Remainder  $\longrightarrow 0$

$$\frac{0}{2)1}$$

(Quotient from previous step)

$$\frac{0}{1}$$

Remainder  $\longrightarrow 1$  (MSD)

Step 3—Rewrite the solution from MSD to LSD:

101112

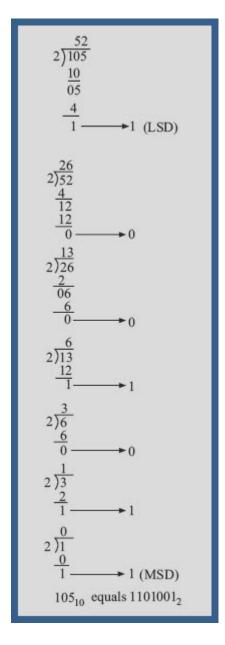

No matter how large the decimal number may be, we use the same procedure. Let's try the problem below. It has a larger dividend:

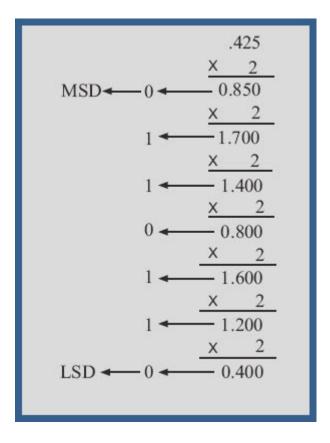

We can convert fractional decimal numbers by multiplying the fraction by the radix and extracting the portion of the product to the *left* of the radix point. Continue to multiply the fractional portion of the previous product until the desired degree of accuracy is attained.

Let's go through this process and convert  $0.25_{10}$  to its binary equivalent:

The *first* figure to the left of the radix point is the MSD, and the last figure of the computation is the LSD. Rewrite the solution from MSD to LSD preceded by the radix point as shown:

.012

Now try converting .625<sub>10</sub> to binary:

As we mentioned before, you should continue the operations until you reach the desired accuracy. For example, convert .425<sub>10</sub> to five places in the binary system:

Although the multiplication was carried out for seven places, you would only use what is required. Write out the solution as shown:

.011012

To convert a mixed number such as  $37.625_{10}$  to binary, split the number into its whole and fractional components and solve each one separately. In this problem carry the fractional part to four places. When the conversion of each is completed, recombine it with the radix point as shown below:

$$37_{10} = 100101_2$$

$$.625_{10} = .1010_2$$

$$37.625_{10} = 100101.1010_2$$

Convert the following decimal numbers to binary:

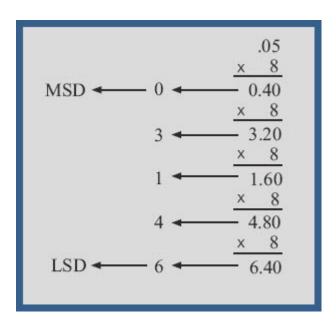

#### 1.6.2 Decimal to Octal

The conversion of a decimal number to its base 8 equivalent is done by the repeated division method. You simply divide the base 10 number by 8 and extract the remainders. The first remainder will be the LSD, and the last remainder will be the MSD.

Look at the following example. To convert  $15_{10}$  to octal, set up the problem for division:

Since 8 goes into 15 one time with a 7 remainder, 7 then is the LSD. Next divide 8 into the quotient (1). The result is a 0 quotient with a 1 remainder. The 1 is the MSD:

$$\begin{array}{c}

\frac{1}{8)15_{10}} \\

\frac{8}{7} \longrightarrow 7 \text{ (LSD)} \\

8)1 \\

\frac{0}{1} \longrightarrow 1 \text{ (MSD)}

\end{array}$$

Now write out the number from MSD to LSD as shown:

The same process is used regardless of the size of the decimal number. Naturally, more divisions are needed for larger numbers, as in the following example:

Convert 264<sub>10</sub> to octal:

$$\begin{array}{c}

33 \\

8)\overline{\smash{)264_{10}}} \\

\underline{24} \\

24 \\

\underline{24} \\

0 \longrightarrow 0 \text{ (LSD)}

\end{array}$$

$$\begin{array}{c}

4 \\

8)\overline{33} \\

\underline{32} \\

1 \longrightarrow 1

\end{array}$$

$$\begin{array}{c}

0 \\

4 \\

0 \longrightarrow 4 \text{ (MSD)}

\end{array}$$

By rewriting the solution, you find that the octal equivalent of  $264_{10}$  is as follows:

To convert a decimal fraction to octal, *multiply* the fraction by 8. Extract everything that appears to the left of the radix point. The first number extracted will be the MSD and will follow the radix point. The last number extracted will be the LSD.

Convert  $0.05_{10}$  to octal:

Write the solution from MSD to LSD:

$.03146_{8}$

You can carry the conversion out to as many places as needed, but usually four or five places are enough.

To convert a mixed decimal number to its octal equivalent, split the number into whole and fractional portions and solve as shown below:

Convert 105.589<sub>10</sub> to octal:

Combine the portions into a mixed number:

151.45548

Convert the following decimal numbers to octal:

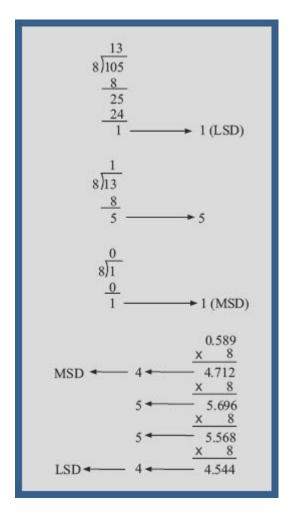

#### 1.6.3 Decimal to Hex

To convert a decimal number to base 16, follow the repeated division procedures you used to convert to binary and octal, only divide by 16. Let's look at an example:

Convert 6310 to hex:

$$\begin{array}{c}

3\\

16)\overline{63_{10}}\\

\underline{48}\\

15_{10}

\end{array}

\longrightarrow F_{16}

\longrightarrow LSD$$

$$\begin{array}{c}

0\\

16)\overline{3}\\

\underline{0}\\

3

\end{array}

\longrightarrow 3_{16}

\longrightarrow MSD$$

Therefore, the hex equivalent of  $63_{10}$  is  $3F_{16}$ .

You have to remember that the remainder is in base 10 and must be converted to hex if it exceeds 9. Let's work through another example:

$$\begin{array}{c}

10 \\

16)\overline{174} \\

\underline{16} \\

14 \\

\underline{0} \\

14_{10}

\end{array}

\longrightarrow E_{16} \longrightarrow LSD$$

$$\begin{array}{c}

0 \\

16)\overline{10} \\

\underline{0} \\

10_{10}

\end{array}

\longrightarrow A_{16} \longrightarrow MSD$$

Write the solution from MSD to LSD:

$AE_{16}$

The solution: .B1EB<sub>16</sub>

Should you have the need to convert a decimal mixed number to hex, convert the whole number and the fraction separately; then recombine for the solution.

Convert the following decimal numbers to hex:

The converting of binary, octal, and hex numbers to their decimal equivalents is covered as a group later in this section.

#### 1.7 BINARY CONVERSION

Earlier in this chapter, we mentioned that the octal and hex number systems are useful to computer programmers. It is much easier to provide data to a computer in one or the other of these systems. Likewise, it is important to be able to convert data from the computer into one or the other number systems for ease of understanding the data.

#### 1.7.1 Binary to Octal

Look at the following numbers:

101110010011012

271158

You can easily see that the octal number is much easier to say. Although the two numbers look completely different, they are equal.

Since 8 is equal to 2<sup>3</sup>, then one octal digit can represent three binary digits, as shown below:

$$0_8 = 000_2$$

$$1_8 = 001_2$$

$$2_8 = 010_2$$

$$3_8 = 011_2$$

$$4_8 = 100_2$$

$$5_8 = 101_2$$

$$6_8 = 110_2$$

$$7_8 = 111_2$$

With the use of this principle, the conversion of a binary number is quite simple. As an example, follow the conversion of the binary number at the beginning of this section.

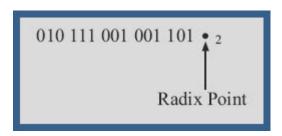

Write out the binary number to be converted. Starting at the radix point and moving left, break the binary number into groups of three as shown. This grouping of binary numbers into groups of three is called binary-coded octal (BCO). Add 0s to the left of any MSD that will fill a group of three:

Next, write down the octal equivalent of each group:

| 010 | 111 | 001 | 001 | 101.2 |

|-----|-----|-----|-----|-------|

| 2   | 7   | 1   | 1   | 5. 8  |

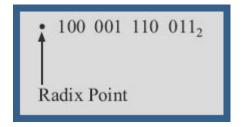

To convert a binary fraction to its octal equivalent, starting at the radix point and moving right, expand each digit into a group of three:

Add 0s to the right of the LSD if necessary to form a group of three. Now write the octal digit for each group of three, as shown below:

| .100 | 001 | 110 | 011.2 |

|------|-----|-----|-------|

| .4   | 1   | 6   | 3 8   |

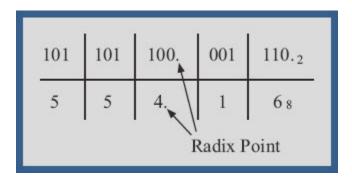

To convert a mixed binary number, starting at the radix point, form groups of three both right and left:

Convert the following binary numbers to octal:

Q65. 10<sub>2</sub>.

Q66. 1010<sub>2</sub>.

Q67. 101111<sub>2</sub>.

Q68. 0.0011<sub>2</sub>.

Q69. 0.110011<sub>2</sub>.

Q70. 110111.010101<sub>2</sub>.

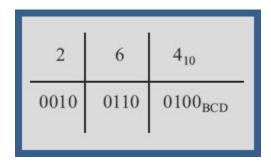

#### 1.7.2 Binary to Hex

The table below shows the relationship between binary and hex numbers. You can see that four binary digits may be represented by one hex digit. This is because 16 is equal to  $2^4$ .

| HEX | <u>\</u> | BINARY |

|-----|----------|--------|

| 0   | =        | 0000   |

| 1   | =        | 0001   |

| 2   | =        | 0010   |

| 3   | =        | 0011   |

| 4   | =        | 0100   |

| 5   | =        | 0101   |

| 6   | =        | 0110   |

| 7   | =        | 0111   |

| 8   | =        | 1000   |

| 9   | =        | 1001   |

| A   | =        | 1010   |

| В   | =        | 1011   |

| C   | =        | 1100   |

| D   | =        | 1101   |

| E   | =        | 1110   |

| F   | =        | 1111   |

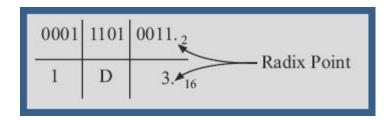

Using this relationship, you can easily convert binary numbers to hex. Starting at the radix point and moving either right or left, break the number into groups of four. The grouping of binary into four bit groups is called binary-coded hexadecimal (BCH).

Convert 111010011<sub>2</sub> to hex:

Add 0s to the left of the MSD of the whole portion of the number and to the right of the LSD of the fractional part to form a group of four.

Convert .111<sub>2</sub> to hex:

In this case, if a 0 had not been added, the conversion would have been .716, which is incorrect.

Convert the following binary numbers to hex:

#### 1.8 OCTAL CONVERSION

The conversion of one number system to another, as we explained earlier, is done to simplify computer programming or interpreting of data.

#### 1.8.1 Octal to Binary

For some computers to accept octal data, the octal digits must be converted to binary. This process is the reverse of binary to octal conversion.

To convert a given octal number to binary, write out the octal number in the following format. We will convert octal  $567_8$ :

Next, below each octal digit write the corresponding three-digit binary-coded octal equivalent:

| 5   | 6   | 78   |

|-----|-----|------|

| 101 | 110 | 1112 |

Solution: 567<sub>8</sub> equals 101 110 111<sub>2</sub>

Remove the conversion from the format:

1011101112

As you gain experience, it may not be necessary to use the block format.

An octal fraction (.123<sub>8</sub>) is converted in the same manner, as shown below:

|               | .1   | 2   | 3    |

|---------------|------|-----|------|

| .001 010 0112 | .001 | 010 | 0112 |

Solution: .123<sub>8</sub> equals .001010011<sub>2</sub>

Apply these principles to convert mixed numbers as well.

Convert 32.25<sub>8</sub> to binary:

| 3   | 2.   | 2   | 58   |

|-----|------|-----|------|

| 011 | 010. | 010 | 1012 |

Solution: 32.25<sub>8</sub> equals 011010.010101<sub>2</sub>

Convert the following numbers to binary:

#### 1.8.2 Octal to Hex

You will probably not run into many occasions that call for the conversion of octal numbers to hex. Should the need arise, conversion is a two-step procedure. Convert the octal number to binary; then convert the binary number to hex. The steps to convert 53.78 to hex are shown below:

| 5   | 3.   | 78   |

|-----|------|------|

| 101 | 011. | 1112 |

Regroup the binary digits into groups of four and add zeros where needed to complete groups; then convert the binary to hex.

| 0010 | 1011. | 11102           |

|------|-------|-----------------|

| 2    | В.    | E <sub>16</sub> |

Solution:  $53.7_8$  equals  $2B.E_{16}$

Convert the following numbers to hex:

#### 1.9 HEX CONVERSION

The procedures for converting hex numbers to binary and octal are the reverse of the binary and octal conversions to hex.

#### 1.9.1 Hex to Binary

To convert a hex number to binary, set up the number in the block format you used in earlier conversions. Below each hex digit, write the four-digit binary equivalent. Observe the following example:

Convert ABC<sub>16</sub> to binary:

Solution:  $ABC_{16} = 1010101111100_2$

#### 1.9.2 Hex to Octal

Just like the conversion of octal to hex, conversion of hex to octal is a two-step procedure. First, convert the hex number to binary; and second, convert the binary number to octal. Let's use the same example we used above in the hex to binary conversion and convert it to octal:

|    | A  |    | H  | 3  | C   | 16   |

|----|----|----|----|----|-----|------|

|    | 10 | 10 | 10 | 11 | 110 | 002  |

| 10 | 01 | 01 | 10 | 1  | 11  | 1002 |

|    | 5  | 2  | 2  | 3  | 7   | 48   |

Convert these base 16 numbers to their equivalent base 2 and base 8 numbers:

#### 1.10 CONVERSION TO DECIMAL

Computer data will have little meaning to you if you are not familiar with the various number systems. It is often necessary to convert those binary, octal, or hex numbers to decimal numbers. The need for understanding is better illustrated by showing you a paycheck printed in binary. A check in the amount of \$10,010,101.00<sub>2</sub> looks impressive but in reality only amounts to \$149.00<sub>10</sub>

#### 1.10.1 Binary to Decimal

The computer that calculates your pay probably operates with binary numbers, so a conversion takes place in the computer before the amount is printed on your check. Some computers, however, don't automatically convert from binary to decimal. There may be times when you must convert mathematically.

For fractional numbers, the decimal value is equal to 1 divided by 2 multiplied by itself the number of times indicated by the exponent. Look at this example:

$$2^{-3} = \frac{1}{2 \times 2 \times 2}$$

or .125<sub>10</sub>

The table below shows a portion of the positions and decimal values of the binary system:

Remember, earlier in this chapter you learned that any number to the 0 power is equal to  $1_{10}$ .

Another method of determining the decimal value of a position is to multiply the preceding value by 2 for whole numbers and to divide the preceding value by 2 for fractional numbers, as shown below:

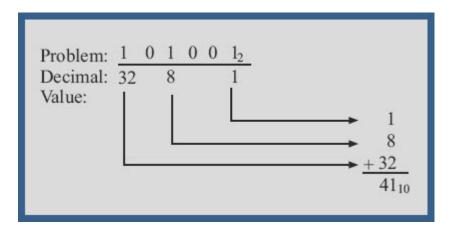

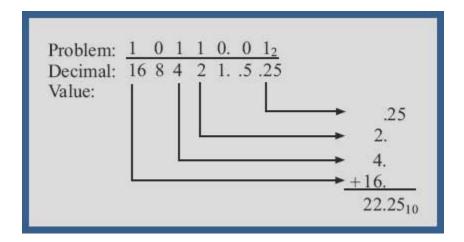

Let's convert a binary number to decimal by using the positional notation method. First, write out the number to be converted; then, write in the decimal equivalent for each position with a 1 indicated. Add these values to determine the decimal equivalent of the binary number. Look at our example:

You may want to write the decimal equivalent for each position as we did in the following example. Add only the values indicated by a 1.

You should make sure that the decimal values for each position are properly aligned before adding. For practice let's convert these binary numbers to decimal:

Q91. 10010<sub>2</sub> Q92. 1111100<sub>2</sub> Q93. 1010101<sub>2</sub> Q94. 0.0101<sub>2</sub> Q95. 0.1010<sub>2</sub> Q96. 1101101.1111<sub>2</sub>

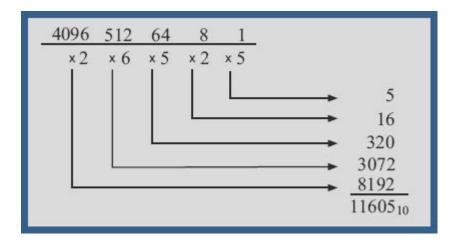

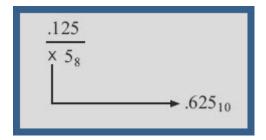

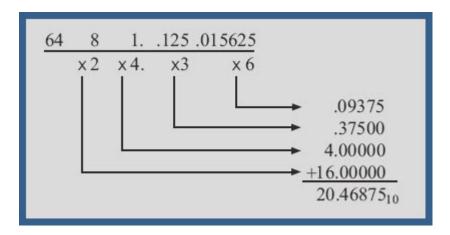

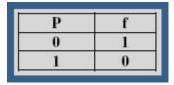

#### 1.10.2 Octal to Decimal